Embedded-Leiterplatten

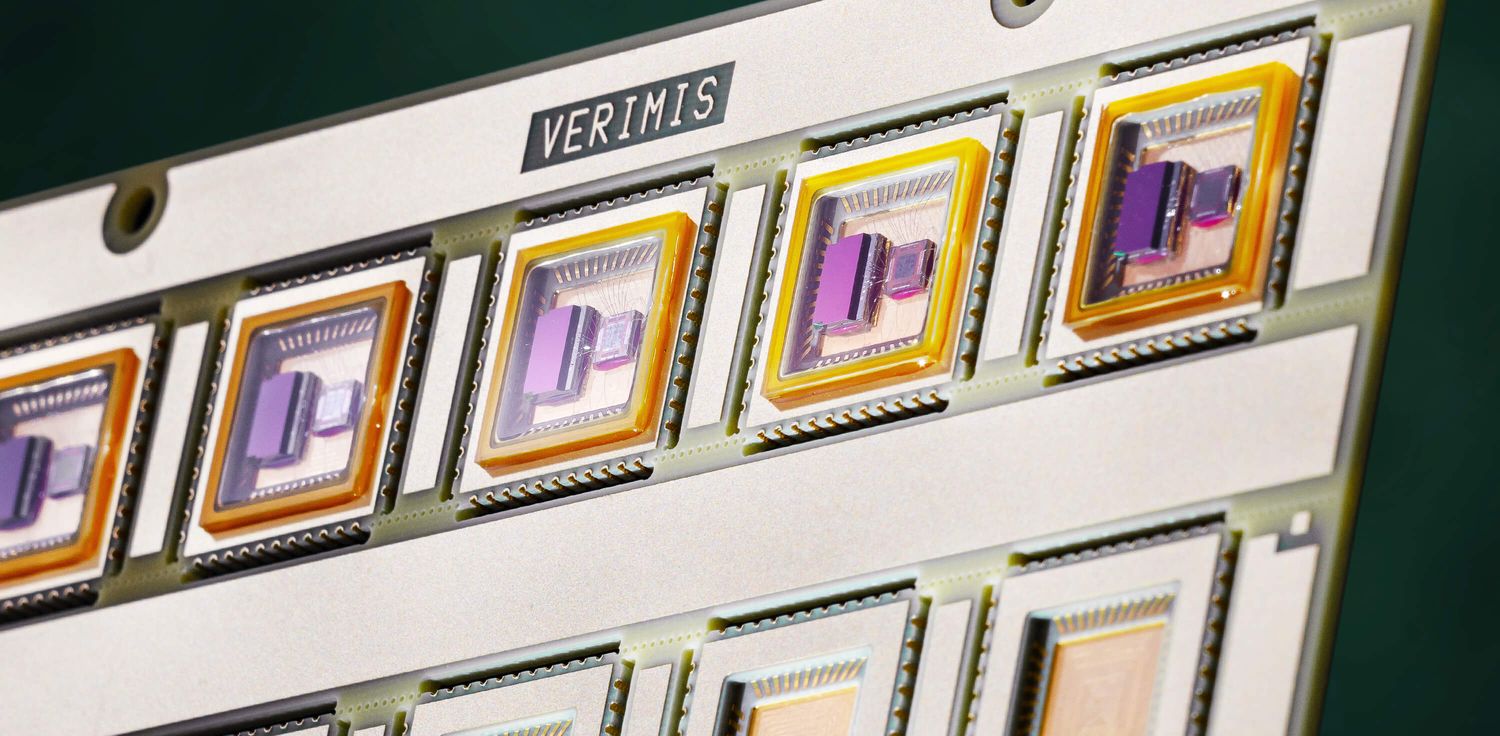

KSG bietet Ihnen mit Embedding-Technologien die passende Lösung für die Integration von aktiven und passiven elektronischen Bauelementen – bis zu einer minimalen Baugröße 01005 und einer maximalen Bauelementhöhe von 2,5 mm.

- Startseite

- Leiterplatten-Technologien

- Embedded Technologie

Ihre Vorteile

- Herstellung anwendungsspezifischer Systeme (System-in-Package, SiP)

- Maximale Miniaturisierung möglich

- Ersatz von Board-to-Board-Lösungen

- Gehäuseersatz/Berührungsschutz

- Optimierte Wärme- und Leistungsverteilung

- Verbesserung des EMV-Schutzes

- Verkürzung der Signalwege

- Erschwertes Reverse Engineering/Plagiatsschutz

- Schutz vor extremen Umwelteinflüssen

- Schutz vor Einflüssen durch Vibration, Stoß und Druck

Gerne unterstützen wir Sie in jeder Phase der Realisierung Ihres Embedding-Projektes.

Kontaktieren Sie hier unser Experten-Team.

Kein Platz auf den Außenlagen? Warum nutzen Sie nicht eine zusätzliche Bestückungsebene im Inneren der Leiterplatte? KSG bietet Ihnen mit Embedding-Technologien die passende Lösung für die Integration von aktiven und passiven elektronischen Bauelementen – bis zu einer minimalen Baugröße 01005 und einer maximalen Bauelementhöhe von 2,5 mm.

| Anzahl der Lagen | ≥ 3 |

| Leiterplattendicke | ≥ 0,25mm für Bestücklage. Gesamtdicke von Bauelementhöhen abhängig |

| Materialien | FR4, andere Basismaterialien auf Anfrage |

| Glasübergangstemperatur | 150°C, 170/180°C |

| Bauelemente | Bauelemente mit Hohlraum oder Elektrolytkondensatoren ungeeignet; Eignung der Bauelemente muss erprobt werden; zur Laseranbindung sind Bauelemente mit Kupferterminals notwendig; maximale Höhe 2,50 mm |

| Besonderheiten PCB | kein HAL Designrules auf Anfrage |

Die angegebenen Werte stellen das maximale Leistungsspektrum dar und können in bestimmten Kombinationen eingeschränkt sein.

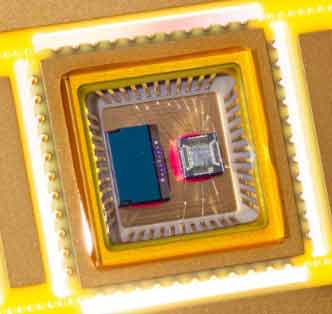

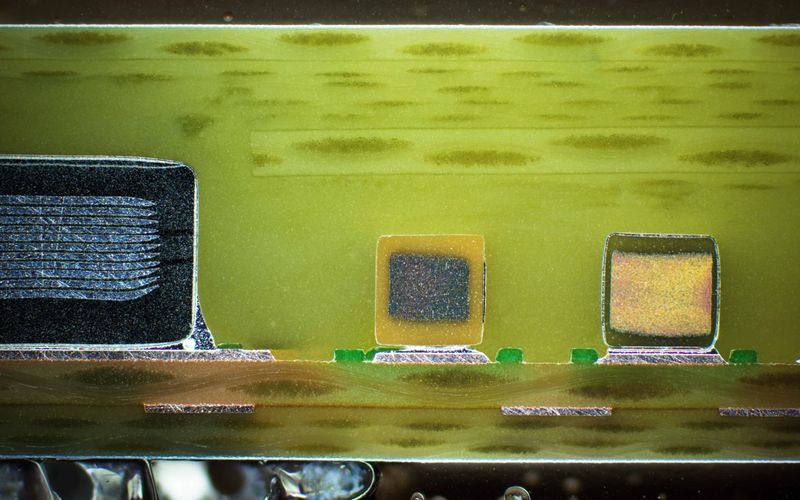

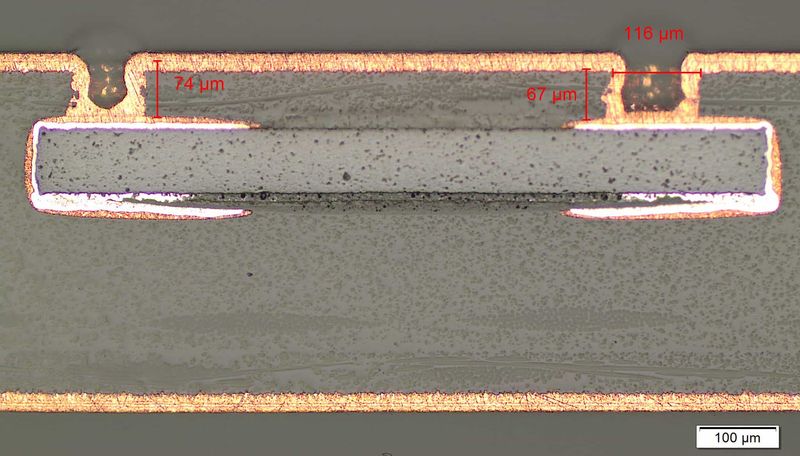

Cavity beschreibt die Herstellung einer oder mehrerer definierter Vertiefungen in der Leiterplatte. Dort werden die Bauelemente mit verschiedenen Verfahren elektrisch und mechanisch kontaktiert.

Mittels des Lötverfahrens werden Bauelemente auf einer Leiterplatte platziert und im anschließenden Laminieren des Multilayers in dessen Verbund eingebettet. Der elektrische Kontakt erfolgt über die Umverdrahtung im Multilayer.

Die Bauelemente werden auf eine Multilayer-Komponente geklebt, in den Verbund einlaminiert und mittels Laser und anschließender Galvanik elektrisch kontaktiert. Die zum Einsatz kommenden Bauelemente besitzen eine für diese Technologie angepasste Anschlusskontaktierung.

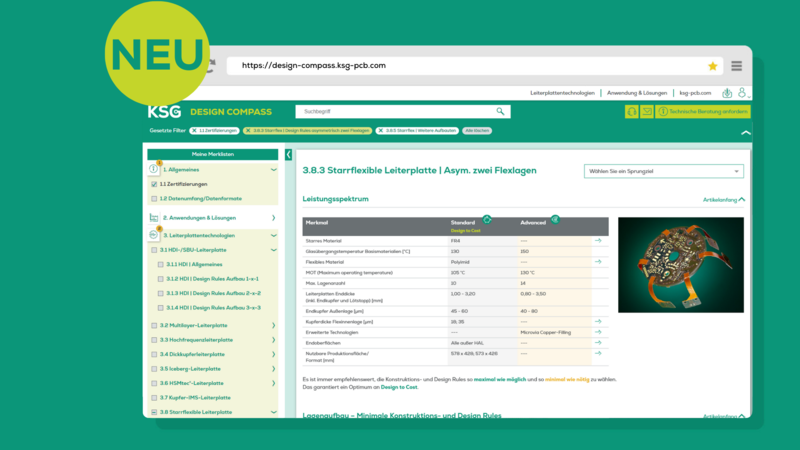

Digital Design Compass

Die smarte Plattform zur schnellen und sicheren PCB-Entwicklung.

- 2 Werke. 1 Plattform. 24/7 erreichbar.

- Designregeln zu allen Technologien

- Praktische Beispiele und Design-to-Cost-Hinweise

Wir haben für Sie alle Parameter in unserem Design Compass gebündelt.

Mit Sicherheit smarter together.

Nutzen Sie den direkten Draht zu den erfahrenen Leiterplattenexperten unseres Technischen Supports. Gerne unterstützen wir Sie in jeder Phase Ihres Projektes.

Wenn zwei Lötebenen nicht genug sind:

maximale Bauteildichte durch Embedding

Herstellung anwendungsspezifischer Systeme (System-in-Package)

Diverse Technologien zur Integration vorhanden